Transistor Evolution: Mula Planar hanggang CFET, Muling Tinutukoy ng Pagsasama ng 3D ang Pag-unlad ng Semiconductor

Para sa higit sa kalahating siglo, ang industriya ng semiconductor ay lumago sa pamamagitan ng pagsunod sa isang simpleng panuntunan: gawing mas maliit ang mga transistor.Ang mga lumiliit na laki ng feature ay naghatid ng mas mataas na performance, mas mababang power, at mas mababang gastos sa bawat transistor.Ngunit ngayon, naabot na ng landas na ito ang pisikal at pang-ekonomiyang limitasyon nito.Tapos na ang panahon ng pure scaling, at isang bagong panahon ng structural innovation at 3D integration nagsimula na.

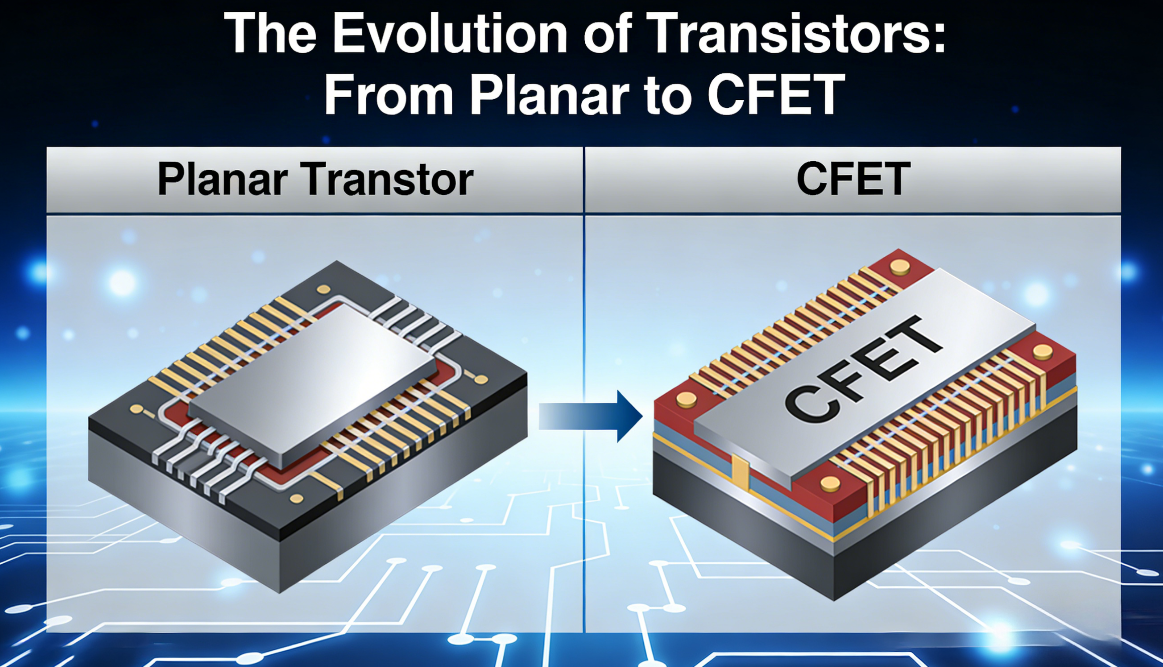

Ang transistor mismo ay sumasailalim sa isang kumpletong rebolusyong arkitektura.Mula sa planar MOSFET hanggang FinFET, mula sa GAA nanosheet hanggang sa CFET stacking, ang bawat hakbang ay kumakatawan sa pagbabago mula sa pag-urong hanggang muling pagtatayo ng transistor sa tatlong dimensyon.Ito ay hindi lamang incremental improvement—ito ay isang kumpletong redefinition kung paano naghahatid ang mga chips ng performance.

Ang Apat na Henerasyon ng Arkitektura ng Transistor

1. Planar Transistor (Tradisyonal na 2D)

Ang klasikong flat structure, kung saan kinokontrol ng gate ang channel mula sa itaas.Nangibabaw ito mula sa mga unang araw hanggang sa 40nm at 28nm.Habang lumiliit pa ang mga sukat, ang kasalukuyang pagtagas at kontrol ng electrostatic ay naging mga hindi malulutas na problema.

2. FinFET (3D Gate Control)

Ang channel ay nagiging isang patayong "palikpik", na ang gate ay bumabalot sa tatlong gilid.Ito ay lubhang nagpapabuti ng electrostatic control, binabawasan ang pagtagas, at nagbibigay-daan sa pag-scale pababa sa 7nm, 5nm, at kahit na 3nm.Ang FinFET ay naging pundasyon ng modernong high-performance chip era.

3. GAA Nanosheet (Gate-All-Around)

Sa 2nm at mas mababa, naabot ng FinFET ang limitasyon nito.Pinapalitan ng GAA ang palikpik ng mga nakasalansan na pahalang na nanowire o mga sheet, na ganap na napapalibutan ng gate.Naghahatid ito ng mas mahusay na kontrol, mas mababang kapangyarihan, at mas mataas na kasalukuyang drive.Ang GAA na ngayon ang pangunahing istraktura para sa 2nm-class na mga chip sa TSMC, Samsung, at Intel.

4. CFET (Complementary FET)

Ang susunod na hangganan: stacking NMOS at PMOS patayo.Ang CFET ay nag-iimpake ng dalawang transistor sa footprint ng isa, na lubhang binabawasan ang lugar at pinapabuti ang density.Ito ang pinakahuling ebolusyonaryong pagtatapos ng transistor scaling bago pumalit ang tunay na 3D system integration.

Bakit Hindi Na Gumagana ang Pag-scale Mag-isa

- Ang mga gastos sa proseso ay tumaas nang husto sa bawat bagong node

- Ang dami ng pagtagas at pisikal na mga hadlang ay nagpapatigas sa mga limitasyon

- Ang pagkaantala ng interconnect at pagkonsumo ng kuryente ay umabot sa bilis ng transistor

- Ang malalaking monolithic chips ay nagdurusa sa mababang ani at mataas na gastos

Napagtanto ng industriya: ang pagganap ay hindi na nagmumula sa mas maliliit na transistor.Ito ay nanggaling sa mas mahusay na koneksyon, mas matalinong arkitektura, at patayong pagsasama.

Ang Bagong Panahon: Tatlong Layer ng 3D Innovation

Ang pag-unlad ng semiconductor ay tinukoy na ngayon ng tatlong dimensyon ng 3D na disenyo:

- 3D Transistor: FinFET, GAA, CFET – pagbuo ng transistor patayo

- 3D Device Stacking: Memory sa logic, hybrid bonding, SRAM stacking

- Pagsasama ng 3D System: Chiplet, 2.5D/3D packaging, interposer-based integration

Magkasama, nabuo nila ang 3D×3D×3D panahon: ang transistor, ang device, at ang system ay nagiging tatlong-dimensional.

DTCO: Ang Bagong Core Competence

Sa pagtatapos ng scaling, Design Technology Co-Optimization (DTCO) nagiging kritikal.Nangangahulugan ito ng co-designing architecture, transistor structure, metal routing, at packaging mula sa simula.Ang pinakamalakas na kumpanya ay hindi na lamang mga pinuno ng proseso—sila ay mga integrator sa antas ng system.

Ang kahusayan ng mga kable, paghahatid ng kuryente, disenyo ng thermal, at density ng bandwidth ay tinutukoy na ngayon ang tunay na pagganap ng produkto.

Ang AI ay ang Ultimate Driving Force

Ang AI at high-performance na computing ay humihingi ng hindi pa nagagawang bandwidth, energy efficiency, at density.Ang mga kinakailangang ito ay hindi matutugunan ng tradisyonal na pag-scale.Nangangailangan sila ng:

- Ultra-high-bandwidth memory-compute interconnect

- Sobrang kahusayan ng enerhiya sa bawat operasyon

- Napakalaking paralelismo at siksik na pagsasama

Pinilit ng AI ang buong industriya na talikuran ang purong pag-scale at yakapin ang buong 3D heterogenous integration.

Konklusyon: Ang Kinabukasan ay Hindi Mas Maliit, Ito ay Mas Mataas

Ang edad ng lumiliit na mga transistor ay kumukupas.Ang kinabukasan ng semiconductors ay hindi tungkol sa pagpapaliit ng mga device—ito ay tungkol sa pagbuo ng mga system mas mataas, mas siksik, at mas matalinong konektado.

Mula Planar hanggang FinFET hanggang GAA hanggang CFET, natapos na ng transistor ang ebolusyon nito.Ang susunod na labanan ay ipaglalaban Pagsasama ng 3D, advanced na packaging, at disenyo sa antas ng system.Dito pagdedesisyonan ang susunod na dekada ng semiconductor leadership.